ПК

Size: a a a

2020 June 22

И как можно писать барьер на ISO C?

Какой барьер?

ПК

И как можно писать барьер на ISO C?

https://en.cppreference.com/w/c/atomic

Вон есть функционал для атомарных операций

Вон есть функционал для атомарных операций

AT

Какой барьер?

Примитив синхронизации, наверное.

ПК

И в чём проблема?

OS

И в чём проблема?

ни в чем. мне было интересно есть ли там такие примитивы. оказывается есть

m

Теперь я совершенно не понимаю что происходит.

Вот цитата из описания ключа:

> /volatile:ms

> Selects Microsoft extended volatile semantics, which add memory ordering guarantees beyond the ISO-standard C++ language. Acquire/release semantics are guaranteed on volatile accesses.

Где здесь acquire/release семантика?

https://godbolt.org/z/izGsPr

Вот цитата из описания ключа:

> /volatile:ms

> Selects Microsoft extended volatile semantics, which add memory ordering guarantees beyond the ISO-standard C++ language. Acquire/release semantics are guaranteed on volatile accesses.

Где здесь acquire/release семантика?

https://godbolt.org/z/izGsPr

ПК

Теперь я совершенно не понимаю что происходит.

Вот цитата из описания ключа:

> /volatile:ms

> Selects Microsoft extended volatile semantics, which add memory ordering guarantees beyond the ISO-standard C++ language. Acquire/release semantics are guaranteed on volatile accesses.

Где здесь acquire/release семантика?

https://godbolt.org/z/izGsPr

Вот цитата из описания ключа:

> /volatile:ms

> Selects Microsoft extended volatile semantics, which add memory ordering guarantees beyond the ISO-standard C++ language. Acquire/release semantics are guaranteed on volatile accesses.

Где здесь acquire/release семантика?

https://godbolt.org/z/izGsPr

Да, у меня получилось только на ARM-е барьеры получить

ПК

>Где здесь acquire/release семантика?

она аппаратная на x86 - в коде не видно

она аппаратная на x86 - в коде не видно

Тогда зачем в msdn это упоминается? Или типа для других архитектур кроме ARM и x86?

m

>Где здесь acquire/release семантика?

она аппаратная на x86 - в коде не видно

она аппаратная на x86 - в коде не видно

По моим представлениям четыре асемблерные инструкции не могут дать атомарный результат:

mov eax, DWORD PTR int volatile x ; x

inc eax

mov DWORD PTR int volatile x, eax ; x

mov ecx, DWORD PTR int volatile x ; x

ПК

Да , для других (кроме x86/64)

ARM бы я не исключал

ARM бы я не исключал

для ARM там как раз в доке исключение, а других платформ кроме x86 и ARM для которых можно собирать с msvc я не знаю

AS

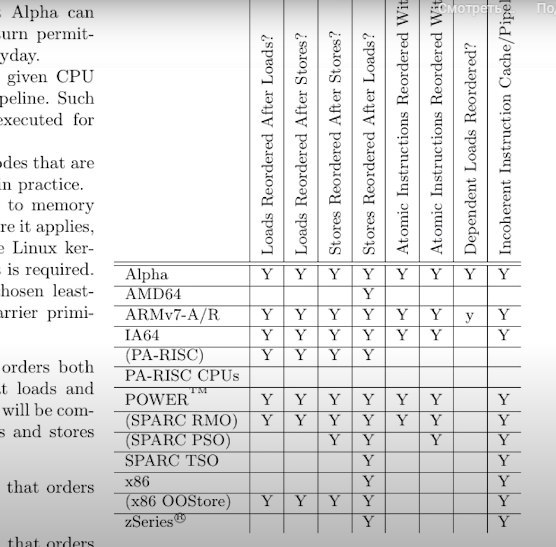

Таблица беспредела процессоров

S

для ARM там как раз в доке исключение, а других платформ кроме x86 и ARM для которых можно собирать с msvc я не знаю

MIPS когда то поддерживался и всякие другие на CE

AS

ПК

Ты можешь объяснить конкретно почему на msdn сказано что volatile в msvc даёт aquire/release семантику, а по коду разницы никакой не видно?

AS

таблица того, что может делать процессор, АRM может делать все что угодно, поэтому барьеры надо будет реализовывать