0N

Size: a a a

2020 July 19

0N

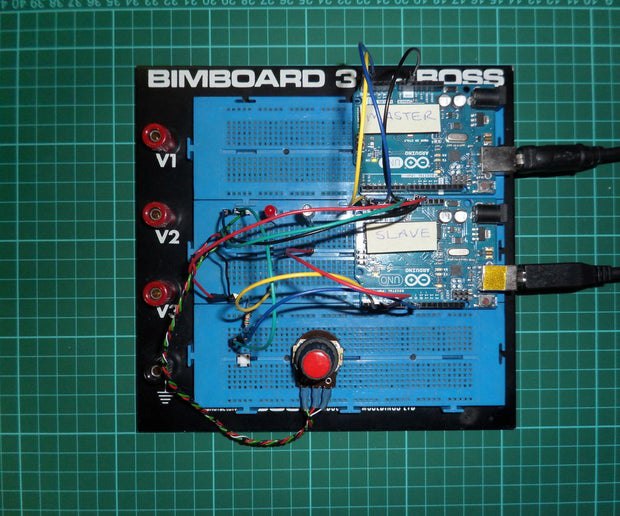

Как правильно эмулировать EEPROM на ардуинке?

Изучил I2C протокол, Master EEPROM Reading, AT24C01, какой запрос отправляет CH341... Но не знаю, как мне отправить обратный ответ, в каком виде он должен быть?

Изучил I2C протокол, Master EEPROM Reading, AT24C01, какой запрос отправляет CH341... Но не знаю, как мне отправить обратный ответ, в каком виде он должен быть?

A

Одной из целей нашей деятельности является популяризация направления разработок на FPGA/ПЛИС среди начинающих разработчиков и инженеров и поэтому прошу Вас максимально распространить это приглашение на мероприятие.

https://fpga-systems.ru/news/skolkovskaja_shkola_sinteza_cifrovykh_skhem_na_verilog/2020-07-19-368

https://fpga-systems.ru/news/skolkovskaja_shkola_sinteza_cifrovykh_skhem_na_verilog/2020-07-19-368

𝔻

Сейчас многие МК содержат на борту ECC.

А Cortex-R - несколько ядер, да синхронно выполняющих программу

А Cortex-R - несколько ядер, да синхронно выполняющих программу

эти ваши Ситары с SECDED (читай: избыточной памятью) и горячим резервом ядер для всяко ASIL (дорого-богато), где принято решать всё "в лоб",

в девайсах по-проще более скромные технологии : блочёк из симбиоза DMA + ядра вычисления хешей для контроля целостности областей памяти

в девайсах по-проще более скромные технологии : блочёк из симбиоза DMA + ядра вычисления хешей для контроля целостности областей памяти

IL

достаточно mmu и микроядра, малый tcb, желательно формально верифицированный и все

0

Иногда заливаю сюда книги из HH, иногда буду свои творчества выкладывать https://t.me/AlienHardware

K

Иногда заливаю сюда книги из HH, иногда буду свои творчества выкладывать https://t.me/AlienHardware

Нижний Новгород? Helly Hansen?

DR

Нижний Новгород? Helly Hansen?

Head Hunter?

K

Норильский Никель

A

эти ваши Ситары с SECDED (читай: избыточной памятью) и горячим резервом ядер для всяко ASIL (дорого-богато), где принято решать всё "в лоб",

в девайсах по-проще более скромные технологии : блочёк из симбиоза DMA + ядра вычисления хешей для контроля целостности областей памяти

в девайсах по-проще более скромные технологии : блочёк из симбиоза DMA + ядра вычисления хешей для контроля целостности областей памяти

Даже в STM32H7 есть ECC на внутренних шинах.

И подобные штуки становятся всё доступнее.

ARM v8m (Cortex-M33) почти все усилия направили на безопасность.

И подобные штуки становятся всё доступнее.

ARM v8m (Cortex-M33) почти все усилия направили на безопасность.