I

Size: a a a

2020 May 21

Надо просто смотреть какие разделы

I

Можно без оты спиффса и прочего влить 4М

SZ

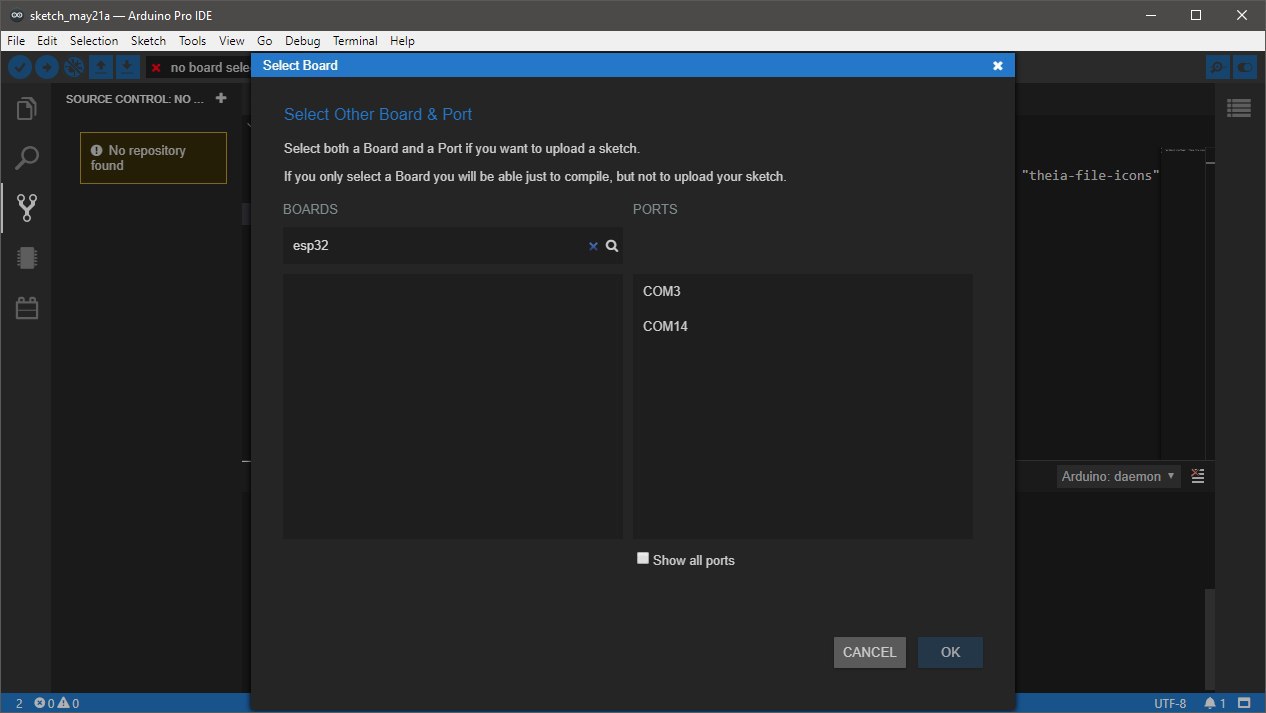

кто знает как сюда esp32 добавить?

I

кто знает как сюда esp32 добавить?

Мануалы по добавлению плат в обычную Arduino IDE тут не подходят?

SZ

чет не нахожу

I

Да в смысле

I

https://randomnerdtutorials.com/installing-the-esp32-board-in-arduino-ide-windows-instructions/

У меня вот например первая ссылка

У меня вот например первая ссылка

SZ

кажись нашел

You have to fo to File... Settings... Open CLI Configuration... and then update the config to add the new board link as shown:

board_manager:

additional_urls: [http://arduino.esp8266.com/stable/package_esp8266com_index.json]

You have to fo to File... Settings... Open CLI Configuration... and then update the config to add the new board link as shown:

board_manager:

additional_urls: [http://arduino.esp8266.com/stable/package_esp8266com_index.json]

AK

видимо, я подошел к финишу

Подробнее:

ESP32 supports multiple external QSPI flash and SRAM chips. More details can be found in Chapter SPI in

the ESP32 Technical Reference Manual. ESP32 also supports hardware encryption/decryption based on AES to

protect developers’ programs and data in flash.

ESP32 can access the external QSPI flash and SRAM through high-speed caches.

• Up to 16 MB of external flash can be mapped into CPU instruction memory space and read-only memory

space simultaneously.

– When external flash is mapped into CPU instruction memory space, up to 11 MB + 248 KB can be

mapped at a time. Note that if more than 3 MB + 248 KB are mapped, cache performance will be

reduced due to speculative reads by the CPU.

– When external flash is mapped into read-only data memory space, up to 4 MB can be mapped at a

time. 8-bit, 16-bit and 32-bit reads are supported.

• External SRAM can be mapped into CPU data memory space. SRAM up to 8 MB is supported and up to 4

MB can be mapped at a time. 8-bit, 16-bit and 32-bit reads and writes are supported.

Note:

After ESP32 is initialized, firmware can customize the mapping of external SRAM or flash into the CPU address space.

ESP32 supports multiple external QSPI flash and SRAM chips. More details can be found in Chapter SPI in

the ESP32 Technical Reference Manual. ESP32 also supports hardware encryption/decryption based on AES to

protect developers’ programs and data in flash.

ESP32 can access the external QSPI flash and SRAM through high-speed caches.

• Up to 16 MB of external flash can be mapped into CPU instruction memory space and read-only memory

space simultaneously.

– When external flash is mapped into CPU instruction memory space, up to 11 MB + 248 KB can be

mapped at a time. Note that if more than 3 MB + 248 KB are mapped, cache performance will be

reduced due to speculative reads by the CPU.

– When external flash is mapped into read-only data memory space, up to 4 MB can be mapped at a

time. 8-bit, 16-bit and 32-bit reads are supported.

• External SRAM can be mapped into CPU data memory space. SRAM up to 8 MB is supported and up to 4

MB can be mapped at a time. 8-bit, 16-bit and 32-bit reads and writes are supported.

Note:

After ESP32 is initialized, firmware can customize the mapping of external SRAM or flash into the CPU address space.

I

кажись нашел

You have to fo to File... Settings... Open CLI Configuration... and then update the config to add the new board link as shown:

board_manager:

additional_urls: [http://arduino.esp8266.com/stable/package_esp8266com_index.json]

You have to fo to File... Settings... Open CLI Configuration... and then update the config to add the new board link as shown:

board_manager:

additional_urls: [http://arduino.esp8266.com/stable/package_esp8266com_index.json]

Это жсон про 8266

SZ

Это жсон про 8266

ну 32 аналогично

I

Andy Korg

Подробнее:

ESP32 supports multiple external QSPI flash and SRAM chips. More details can be found in Chapter SPI in

the ESP32 Technical Reference Manual. ESP32 also supports hardware encryption/decryption based on AES to

protect developers’ programs and data in flash.

ESP32 can access the external QSPI flash and SRAM through high-speed caches.

• Up to 16 MB of external flash can be mapped into CPU instruction memory space and read-only memory

space simultaneously.

– When external flash is mapped into CPU instruction memory space, up to 11 MB + 248 KB can be

mapped at a time. Note that if more than 3 MB + 248 KB are mapped, cache performance will be

reduced due to speculative reads by the CPU.

– When external flash is mapped into read-only data memory space, up to 4 MB can be mapped at a

time. 8-bit, 16-bit and 32-bit reads are supported.

• External SRAM can be mapped into CPU data memory space. SRAM up to 8 MB is supported and up to 4

MB can be mapped at a time. 8-bit, 16-bit and 32-bit reads and writes are supported.

Note:

After ESP32 is initialized, firmware can customize the mapping of external SRAM or flash into the CPU address space.

ESP32 supports multiple external QSPI flash and SRAM chips. More details can be found in Chapter SPI in

the ESP32 Technical Reference Manual. ESP32 also supports hardware encryption/decryption based on AES to

protect developers’ programs and data in flash.

ESP32 can access the external QSPI flash and SRAM through high-speed caches.

• Up to 16 MB of external flash can be mapped into CPU instruction memory space and read-only memory

space simultaneously.

– When external flash is mapped into CPU instruction memory space, up to 11 MB + 248 KB can be

mapped at a time. Note that if more than 3 MB + 248 KB are mapped, cache performance will be

reduced due to speculative reads by the CPU.

– When external flash is mapped into read-only data memory space, up to 4 MB can be mapped at a

time. 8-bit, 16-bit and 32-bit reads are supported.

• External SRAM can be mapped into CPU data memory space. SRAM up to 8 MB is supported and up to 4

MB can be mapped at a time. 8-bit, 16-bit and 32-bit reads and writes are supported.

Note:

After ESP32 is initialized, firmware can customize the mapping of external SRAM or flash into the CPU address space.

Помоему это слишком через чур раздутый ответ

I

ну 32 аналогично

Ну да : ) Просто обратил внимание

I

Кстати первый раз в жизни увидел Arduino PRO ide

AK

Помоему это слишком через чур раздутый ответ

Супер раздутый? :)

I

Andy Korg

Супер раздутый? :)

Супер пупер

D

platformio наше всё

I

platformio наше всё

Вообще, скрин этой ардуино про иде до боли напоминает vs code, но это не точно

D

так она умеет ставица в vscode