SZ

Size: a a a

2019 December 13

Но сд карта не работает на такой скорости. Поставил 1 000 000. Заработало

Я тут ошибся, я поставил 10 000 000

YT

Я тут ошибся, я поставил 10 000 000

Ну тогда всего в два раза. Такое "бывает" люди пишут.

SZ

Подытожим... Надо попробовать распаять не модуль микро сиди, а пластмассовый адаптер SD - microSD.

YT

Подытожим... Надо попробовать распаять не модуль микро сиди, а пластмассовый адаптер SD - microSD.

И отключить периферию, без всего затестить

SZ

И карточку скоростную, отключать экран не буду

YT

И карточку скоростную, отключать экран не буду

YT

Удивительно но да, UHS может не лишней быть. Только не все одинаково полезные. Там тесты по ссылке норм так

YT

👆 вообще все не просто - про разные частоты можно говорить

YT

one is the clock generator which drives SDMMC peripheral,

* it can be configured using SDMMC.clock register. It can generate

* frequencies 160MHz/(N + 1), where 0 < N < 16, I.e. from 10 to 80 MHz.

* - 4 clock dividers inside SDMMC peripheral, which can divide clock

* from the first stage by 2 * M, where 0 < M < 255

* (they can also be bypassed).

*

* For cards which aren't UHS-1 or UHS-2 cards, which we don't support,

* maximum bus frequency in high speed (HS) mode is 50 MHz.

* Note: for non-UHS-1 cards, HS mode is optional.

* Default speed (DS) mode is mandatory, it works up to 25 MHz.

* Whether the card supports HS or not can be determined using TRAN_SPEED

* field of card's CSD register.

* it can be configured using SDMMC.clock register. It can generate

* frequencies 160MHz/(N + 1), where 0 < N < 16, I.e. from 10 to 80 MHz.

* - 4 clock dividers inside SDMMC peripheral, which can divide clock

* from the first stage by 2 * M, where 0 < M < 255

* (they can also be bypassed).

*

* For cards which aren't UHS-1 or UHS-2 cards, which we don't support,

* maximum bus frequency in high speed (HS) mode is 50 MHz.

* Note: for non-UHS-1 cards, HS mode is optional.

* Default speed (DS) mode is mandatory, it works up to 25 MHz.

* Whether the card supports HS or not can be determined using TRAN_SPEED

* field of card's CSD register.

RE

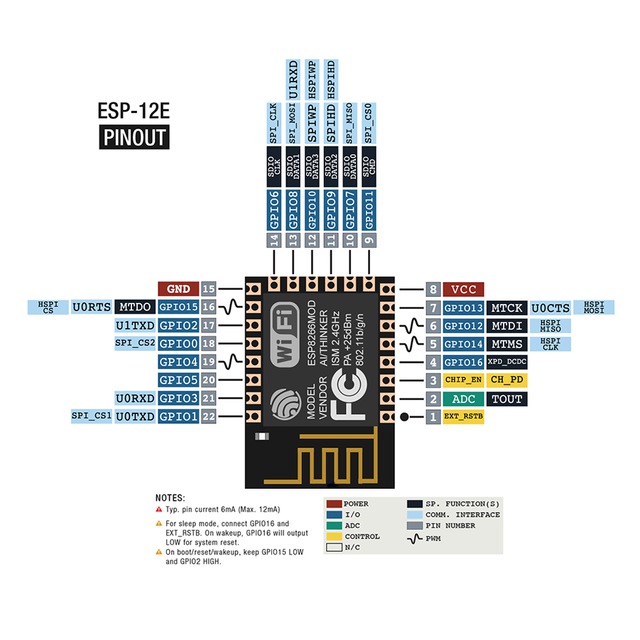

Здравствуйте. Поделитесь пожалуйста скетчем на 8266 включение реле по mqtt - главное чтобы отоброжало состояние реле и жизинь самого клиента

AK

Здравствуйте. Поделитесь пожалуйста скетчем на 8266 включение реле по mqtt - главное чтобы отоброжало состояние реле и жизинь самого клиента

на ардуине нет. есть на си

RE

Andy Korg

на ардуине нет. есть на си

ардуино ide смогу?

AK

ардуино ide смогу?

не знаю :(

RE

Ну хорошо... Высылайте

AK

AndyKorg/LedSmart: smart lamp on the door. on esp8266-rtos sdk

https://github.com/AndyKorg/LedSmart

https://github.com/AndyKorg/LedSmart

EG

550,17 руб. 5%СКИДКА | Датчик газа для измерения внутреннего воздуха SGP30 многопиксельный газовый датчик TVOC/eCO2 Датчик качества воздуха формальдегида углекислого газа Тестер

https://s.click.aliexpress.com/e/bcVohvhu

https://s.click.aliexpress.com/e/bcVohvhu

EG

Интересный датчик кто нибудь брал?

D

интересный, надо будет заказать

D

заказал, но придёт только в январе :(